近年来,超声波在工业中的应用不断涌现,比如超声波探伤,超声波清洗等等。伴随着超声研究的热门,如何有效的产生符合要求的超声波功率源也变的迫切起来,其性能特点直接影响着超声的研究工作。上述研究需要超声波具有高分辨率、高稳定性、大功率、频率大范围可调等特点,为此,本文提出了一种基于现场可编程逻辑门阵列(FPGA)的DDS技术用来产生超声波功率源的方案,并已将其应用在实际的声学研究中。

一.系统原理及特点

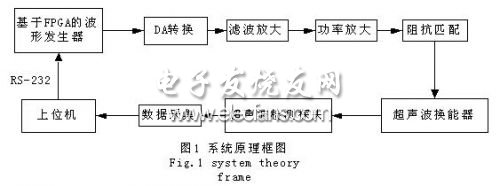

系统原理如图1所示。用现场可编程逻辑门阵列(FPGA)芯片,通过直接数字频率合成(DDS)技术产生频率为1kHz~100kHz的波形信号;功率放大采用功放模块;功率放模块的输出通过输出变压器和电感组成的匹配网络驱动压电换能器激发超声波。

本系统的主要特点有 :

(1)用数字DDS技术产生波形信号,分辨率高、稳定性好、频率范围大,系统频率不会随工作时间出现漂移。

(2)功率放大功放模块,系统性能稳定,功率可达500W左右。

(3)系统通过上位机串行口输入控制数据或接收反馈,操作灵活方便。

二.系统硬件实现

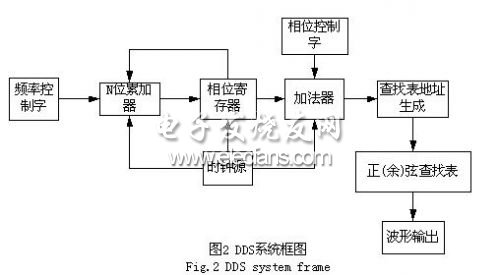

2.1 DDS原理及电路实现

DDS技术是一种用数字控制信号的相位增量技术,具有频率分辨率高、稳定性好、可灵活产生多种信号的优点。基于DDS的波形发生器是通过改变相位增量寄存器的值△phase(每个时钟周期的度数)来改变输出频率的。如图2所示,每当N位全加器的输出锁存器接收到一个时钟脉冲时,锁存在相位增量寄存器中的频率控制字就和N位全加器的输出相加。在相位累加器的输出被锁存后,它就作为波形存储器的一个寻址地址,该地址对应的波形存储器中的内容就是一个波形合成点的幅度值,然后经D/A转换变成模拟值输出。当下一个时钟到来时,相位累加器的输出又加一次频率控制字,使波形存储器的地址处于所合成波形的下一个幅值点上。最终,相位累加器检索到足够的点就构成了整个波形。

DDS的输出信号频率由下式计算:

Fout=(△phase&TImes;FCLK)/2N (1)

DDS的频率分辨率定义为:

Fout=FCLK/2N (2)

由于基准时钟的频率一般固定,因此相位累加器的位数决定了频率分辨率,位数越多,分频率越高。

2.2 DDS的FPGA实现

FPGA(现场可编程逻辑门阵列)是从80年代中期开始出现的一种新的可编程器件,它们的编程方式先进高速,可以在线编程修改,一般工作频率可以达到100MHz,所以在数字电路设计领域得到越来越广泛的应用。本系统中采用Altera公司的cyclone系列的FPGA进行DDS的设计,采用的芯片是EP1C3T144C8。

(1)相位字寄存器

它是一个24位的并行输入并行输出寄存器,用来存放24位的相位值,即频率控制字,系统工作时,可以通过上位机的串口输入频率控制字。

(2)相位累加器

相位累加器用于对代表频率的相位字进行累加运算,相位字的值决定了输出信号的频率。

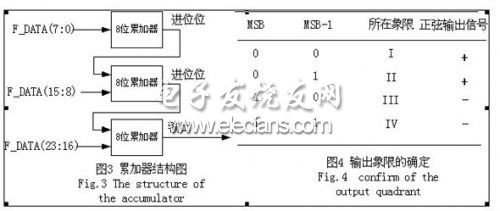

如图3,本系统中的累加器采用的是24位的结构,如果直接采用很宽位数的加法器构成累加器,则加法器的延时会大大的限制累加器的操作速度,所以采用的是3个8位的累加器级连的结构,每一级采用一个小的累加器实现部分位的累加,然后再将进位值传给下一级做进一步的累加,从而提高了系统的运算速度。

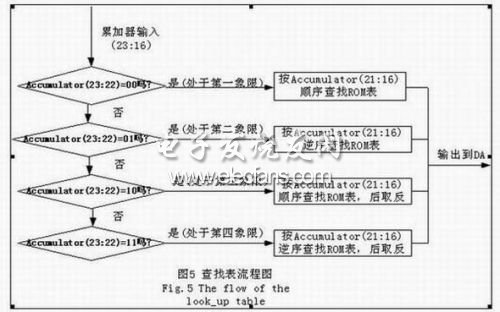

(3)查找表的结构

本系统将累加器的高8位作为查表表的地址,其中高两位用来确定象限。

在FPGA中,正弦表是用ROM来实现的,为了节省资源,考虑到正弦波的对称性,实际上只需要存储正弦值在第一象限的值,如图4所示。查找表的逻辑流程如图5。